Home >> Blog >> 什麼是 metastability?

什麼是 metastability?

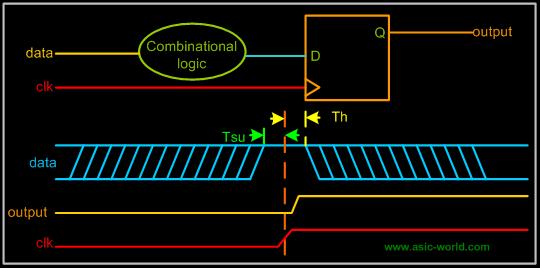

每當任何觸發器中存在建立和保持時間違規時,它都會進入其輸出不可預測的狀態:這種狀態稱為metastability(準穩定狀態);在metastability結束時,觸發器穩定到“1”或“0”。這整個過程被稱為metastability。下圖中 Tsu 是建立時間,Th 是保持時間。每當輸入信號 D 不滿足給定 D 觸發器的 Tsu 和 Th 時,就會出現metastability。

當觸發器處於metastability時,其輸出在“0”和“1”之間振盪,如下圖所示(此處觸發器輸出穩定為“0”)。安定下來需要多長時間,取決於觸發器的技術。

如果我們深入觀察觸發器內部,我們會發現當觸發器建立和保持時間被違反時,就會達到準穩定狀態。假設使用正沿觸發的“D”型觸發器,當觸發器時鐘的上升沿發生在觸發器的 D 輸入導致其主鎖存器轉換的時間點時,觸發器極有可能最終處於準穩定狀態。這個上升時鐘導致主鎖存器在從鎖存器打開時嘗試捕獲其當前值,從而允許 Q 輸出跟隨主控器的“鎖存”值。最完美的“捕獲”準穩定狀態(在山頂上)導致觸發器將自身解決到穩定狀態之一所需的最長時間。

它會在這種狀態下停留多久?

上圖所示狀態的相對穩定性表明,邏輯 0 和邏輯 1 狀態(位於山腳下)比位於山頂的稍微穩定的狀態穩定得多。理論上,在這個準穩定的山頂狀態下的觸發器可以無限期地保持在那裡,但實際上它不會。就像最輕微的氣流最終會導致所示山丘上的球從一側或另一側滾下一樣,熱噪聲和感應噪聲將推動觸發器的狀態,使其從準穩定狀態移動到邏輯 0 或邏輯 1 狀態。

發生metastability的情況有哪些?

正如我們所看到的,每當建立和保持違反時間發生時,就會發生metastability,因此我們必須查看信號何時違反此時序要求:

- 當輸入信號為異步信號時。

- 當時鐘偏差/擺幅太大時(上升和下降時間超過容許值)。

- 當連接在兩個不同頻率或相同頻率但具有不同相位的兩個域時。

- 當組合延遲使得觸發器數據輸入在關鍵窗口(建立+保持窗口)中發生變化時

什麼是 MTBF?

MTBF 是平均故障間隔時間,這是什麼意思?MTBF 為我們提供了有關特定元素失敗頻率的信息,或者換句話說,它提供了兩次連續失敗之間的平均時間間隔。下圖顯示了觸發器的典型 MTBF,並給出了 MTBF 方程。我不想在這裡推導出 MTBF 方程 :-)

那麼如何避免metastability呢?

實際上,如果不使用複雜的自定時電路,就無法避免metastability和同步異步輸入中時鐘到 Q 延遲的增加。所以一個更合適的問題可能是“我如何容忍metastability? ”

在最簡單的情況下,設計人員可以通過確保時鐘週期足夠長以允許準穩定狀態的分辨率以及通向下一個觸發器的路徑中可能存在的任何邏輯的延遲來容忍metastability。鑑於大多數現代設計的性能要求,這種方法雖然簡單,但很少實用。

容忍metastability的最常見方法是在同步器中添加一個或多個連續的同步觸發器。這種方法允許第一個同步觸發器中的metastability事件在整個時鐘週期(第二個觸發器的建立時間除外)中自行解決。然而,這確實增加了同步邏輯觀察輸入變化的延遲。

這些方法都不能保證metastability不能通過同步器;他們只是將概率降低到實際水平。

在定量方面,如果特定觸發器在給定時鐘速率和輸入轉換速率的上下文中的平均故障間隔時間 (MTBF) 為 33.33 秒,那麼用於同步輸入的兩個此類觸發器的 MTBF 將為(33.33* 33.33) = 18.514 分鐘。好吧,我採用了人類歷史上設計過的最糟糕的觸發器:-)。下圖顯示瞭如何串聯兩個觸發器來實現這一點以及由此產生的 MTBF。

一般,

- 我們可以使用metastability硬化觸發器

- 級聯兩個或三個 D 觸發器(兩級或三級同步器)。